DSP Digital Signal — Deterministic Design, Tooling, Six Exact Part Numbers, and Factory-Ready Practices

Posted in CategoryAgriculture Discussion-

Yyic 5 months ago

Yyic 5 months agoDSP Digital Signal — A Single, Production-First Field Guide for Deterministic Engineering in 2025

From voice arrays and beamforming to field-oriented control and instrumentation, modern products need silicon that guarantees bounded latency and sample-accurate I/O. This single-part guide consolidates architecture, timing, memory locality, verification, and factory readiness into one coherent narrative you can drop into design reviews and bring-up plans..

Readers who want a concise refresher on fundamentals—MAC pipelines, circular buffers, saturation arithmetic, block floating-point, overlap-save convolution—can skim the encyclopedia overview of DSP techniques before diving into the production details below.

How to use this page. It is a production-first field guide. We define timing anchors, DMA choreography, scratchpad/cache policy, numerical guardrails, verification assets, and factory practice. Examples are grounded in six complete part numbers whose first mention links to the dsp digital signal official vendor page.Six Exact, Production-Grade Part Numbers

Full Part Number Vendor Class Why It’s Useful Typical Fits TMS320C6657CZHK Texas Instruments Dual C66x floating/fixed DSP High-throughput VLIW cores with queue DMA; excels at multi-channel filter banks and beamforming with bounded latency. Telecom channelization, wideband beamforming, high-end audio post ADSP-21569KCPZ Analog Devices SHARC+ floating-point DSP Large on-chip SRAM + deterministic DMA; ideal for frame-based audio, room correction, instrumentation FFT engines. Pro audio DSP, acoustic correction, measurement rigs MC56F83677VLH NXP 56F8xxx digital signal controller Fixed-point MAC, high-res PWM/ADC trigger matrix; instant-on, low-jitter control loops. FOC motor drives, PFC/SMPS, industrial motion control dsPIC33CH512MP508-I/PT Microchip Dual-core dsPIC digital signal controller Master/secondary cores partition real-time control vs. comms/telemetry; mature Q15/Q31 libraries. Drives and PSUs with deterministic control + auxiliary tasks STM32H563ZIT6 STMicroelectronics MCU with DSP/FPU (Cortex-M33) DSP/SIMD + TCM-like SRAM; HRTIM/ADC for control, SAI/I²S for audio side-chains, robust DMA fabric. Mixed control + DSP, connected edge nodes R7FA6M5BH3CFC Renesas RA6M5 MCU with DSP intrinsics M33 + DSP intrinsics, ample SRAM, and long-lifecycle security/OTA; deterministic time windows between comms bursts. Industrial gateways, sensor fusion, real-time filtering

1) Determinism Starts with a Timing Contract

Pick one anchor for the whole graph and write it in the spec: PWM/timer edges for control plants, frame boundaries for audio, queue ticks for channelizers, or cycle-budgeted threads on many-core MCUs. The anchor defines your ceilings: worst-case compute per anchor, end-to-end latency, and maximum jitter (in samples or nanoseconds). Average times do not ship products; ceilings do.

Prove the contract with GPIO strobes at ISR entry/exit and long-soak trace histograms. Store screenshots and CSVs beside the timing spec. For audio, strobe the frame ISR and the DAC write on separate pins; the delta is your authoritative input-to-output delay. For control, correlate ISR timing strobes with current probes on the phase legs to verify causality.

Pocket budgets you can remember

- Audio @ 48 kHz, 32-sample frames: 0.667 ms. Target ≤ 0.35 ms steady; ≤ 0.45 ms with overlays/preset swaps; leave ≥ 0.2 ms for cache/pathology events.

- FOC @ 20 kHz PWM: 50 µs. Allocate ≤ 20 µs to Clarke/Park → PI(d,q) → SVPWM; ≤ 5 µs to diagnostics; ≥ 20 µs slack for EMI/interrupts.

- Multi-core channelizer: Per-core green/yellow/red bands; throttle nonessential tasks before sustained yellow becomes red.

2) Memory Locality & DMA Choreography

Hot loops and tight buffers belong in the closest memory (L1/TCM/on-chip SRAM). Treat external SDRAM as bulk storage—never the real-time path. Let DMA own long moves: ping-pong buffers and scatter–gather descriptors overlap filling and processing without touching in-flight data. Avoid pointer chasing in hot loops: precompute stride tables and address maps during init.

Streaming templates you can reuse

- Ping-pong + scatter–gather: While DMA fills buffer A, the core processes buffer B pinned in fast memory. On interrupt, swap roles and pre-post the next descriptor a frame ahead to avoid bubbles.

- TDM de-interleave without inner-loop math: Use stride-aware descriptors so each channel lands in a contiguous sub-buffer; the core receives already de-interleaved frames.

- Cache policy that won’t bite later: On C66x/SHARC+, lock hot code/data into on-chip SRAM and stage overlays outside real-time windows. On M33-class MCUs, keep inner loops in TCM-like SRAM and mark DMA buffers as device/non-cacheable or fence transfers.

3) Numerics Discipline—Fixed, Float, Multirate

Fixed-point rules that prevent midnight field calls

- Commit house formats: Q15 for currents/voltages; Q31 for energy/integrators. Enforce conversion macros globally; never silently mix formats.

- Use transposed DF-II with saturation for IIR biquads; inject small dither during verification to surface limit cycles.

- Long FIR/FFT chains use block floating with explicit guard bits; maintain ≥ 12 dB internal headroom.

Floating-point hygiene

- Pin rounding and FMA policy; keep them constant across builds and compilers.

- Flush-to-zero for denormals to prevent stalls and noise-floor “hair.”

- Consider FP32 compute + FP16 coefficient storage under cache pressure; document SNR impact.

ASRC and clock-domain crossings (audio)

- Pick a single render domain (e.g., 48 kHz). Convert once at ingress; never stack ASRCs mid-graph.

- Size guard bands for worst-case ppm drift over hours; log under/over-flows to catch mis-sizing.

- Do not re-parent PLLs mid-stream; treat clocks like RF and verify jitter at the pins.

4) Device-Specific Playbooks (Actionable)

TMS320C6657CZHK — Beamforming/Channelization Spine

- Anchor: Descriptor/queue ticks. Stripe channels per core; replicate coefficient banks to avoid cross-core contention.

- DMA: Queue DMA with pre-posted descriptors and watchdogs on underflow/overflow; record per-stage latency histograms.

- Debug: GPIO strobes around DDC → decimate → FFT → weight → sum. Keep twiddles in on-chip memory to avoid DRAM thrash.

ADSP-21569KCPZ — Audio/Measurement Workhorse

- Anchor: Frame ISR. Lock hot code/data to on-chip SRAM; compile block graphs in deterministic order.

- ASRC: Only at ingress; single render clock domain. Final limiter immediately pre-DAC.

- Verification: Group-delay plots, THD+N/SNR, intelligibility proxies (where licensed), and null tests for beamformers.

MC56F83677VLH — FOC and PSUs

- Anchor: PWM center. Sample ADC at the flat point; compute Clarke/Park → PI(d,q) → inverse Park → SVPWM before the next edge.

- Protection: Cycle-by-cycle current limit outside the PI window; safe duties on fault; watchdog coverage.

- Calibration: Dead-time trims, shunt gains/offsets, and Kp/Ki tables in flash with CRC + schema version.

dsPIC33CH512MP508-I/PT — Dual-Core Partitioning

- Split roles: Secondary core runs real-time control; master core handles comms/telemetry/OTA.

- Fixed-point hygiene: Q15/Q31 macros, anti-windup via back-calculation, Monte-Carlo sweeps for coefficient extremes.

- Bring-up: Safe PWM defaults at boot; brownout behavior documented and tested.

STM32H563ZIT6 — Mixed Control + DSP

- Anchor: HRTIM + ADC for control, SAI/I²S frames for audio side-chains.

- Locality: Place inner loops in TCM-like SRAM; mark streaming buffers device/non-cacheable or fence transfers.

- Risk: Cache-induced jitter; fix via TCM placement, buffer alignment, and disciplined DMA descriptors.

R7FA6M5BH3CFC — Long-Life Edge Nodes

- Strength: DSP/SIMD intrinsics with strong security/OTA; ample SRAM for deterministic windows.

- Pattern: Slice DSP work between comms bursts; DMA fills/drains rings; compute on compact windows only.

- Diagnostics: Telemetry page exposing ISR histograms, limiter hits, and temperature derates.

5) Reusable Pipelines (Audio, Control, Measurement)

Two-Mic Voice Chain (Low-Latency)

- Front-end: HPF → per-mic trims (±0.2 dB) → soft clip for catastrophic frames.

- Beamformer: GSC for fixed geometry; MVDR for adaptive nulls. Fractional-delay filters for sub-sample alignment.

- AEC: Partitioned-block canceller with double-talk detection separate from VAD; freeze adaptation on strong near-end.

- NR: Spectral subtraction/Wiener with minima-controlled trackers; cap musical noise and preserve transients.

- QA: Intelligibility proxies (where licensed), SNR improvement, lip-sync error < 20 ms.

FOC Loop (20–40 kHz ISR Windows)

- PWM center aligned → ADC sample at flat point → Clarke/Park → PI(d,q) with anti-windup → inverse Park → SVPWM.

- Prove ISR budget via GPIO and correlate with current probes/torque response.

- Derating tables for temperature and bus voltage; trims stored with CRC + versioning.

Multichannel FFT Analyzer / Channelizer

- Overlap-save convolution sized to cache/TCM; pre-twiddle in on-chip SRAM; stride-aware descriptors de-interleave channels.

- The CPU touches hot bins only; bulk moves are DMA-owned.

- Drift checks: ppm/clock sanity with analyzer captures; logs archived in the repo.

6) Verification Assets That Track Perception and Stability

Audio & Voice

- Golden content: swept sines, multitone IMD, pink noise, near/far-field speech corpora.

- Metrics per build: THD+N, SNR, group-delay ripple, intelligibility proxies.

- Limiter QA: high-crest-factor content; multiband limiters must avoid “pumping.”

Control & Power

- Step/ramp/load-dump across temperature/supply corners; capture settling/overshoot/undershoot.

- ISR histograms over six-hour soaks; investigate any drift toward headroom before release.

Arrays & Beamforming

- Per-band beam maps with null depths and sidelobe levels; per-element gain/phase trims checksummed.

- Field diagnostic that verifies trims without lab gear; circular capture around triggers for returns.

7) Risk Ledger: What Breaks (and How to Preempt It)

Symptom Likely Root Cause Preventive Practice Emergency Fix Random clicks/glitches Cache line thrash on DMA buffers Non-cacheable DMA regions; hot code in L1/TCM Fence caches around transfers; increase frame size Overshoot at hot Gain scaling assumes room temp; ADC offset drift Temperature-indexed tables; offset trims in NVM Reduce loop bandwidth; clamp integrators EDMA underruns Descriptors not pre-posted; clock ppm drift Pre-post a frame ahead; single render domain Widen guard bands; lower frame cadence Throughput OK, jitter visible External DRAM contention Keep hot buffers on-chip; stagger burst masters Smaller bursts; emergency cache locking

8) Factory Bring-Up, Calibration, and Serviceability

Power & Clock DVT

- Scope rail ramps and POR thresholds at cold/room/hot; archive screenshots with schematics.

- Measure oscillator/PLL jitter and lock times; specify ppm and phase-noise targets explicitly.

Boundary-Scan & Fixtures

- Per-SKU vectors that exercise I²S/TDM lanes and GPIO direction; pass/fail masks embedded in fixtures.

- Digital-amp SKUs: load banks with worst-case impedance dips; log current/thermal telemetry during burn-in.

Audio & Control Trims

- Audio: Level/offset trims, inter-channel delay alignment, DAC linearity; store with CRC + version.

- Control: ADC gain/offset, PWM dead-time, phase alignment; validate with scripted steps/inertia sweeps.

OTA & Field Diagnostics

- Atomic update: shadow bank + CRC; automatic rollback on failure.

- Telemetry schema: limiter hits, ISR overruns, temperature derates, ASRC under/over-flows; circular log readable by service tools.

9) End-to-End Examples (Copy, Adapt, Ship)

Voice Bar (Two-Mic, Low-Latency)

- Frame = 16 samples @ 16 kHz: HPF → per-mic AGC → beamformer (GSC) → AEC → NR → VAD.

- Headroom map: −12 dBFS nominal, +1 dBFS final limiter; presets (quiet/office/car) as versioned blobs.

- QA gates: intelligibility drop < 2% vs. golden; lip-sync < 20 ms; limiter hit counts logged.

FOC Drive (DSC or dsPIC)

- Anchor ISR at PWM center; ADC sample at quiet point; complete transforms and PI inside 20 µs @ 20 kHz.

- Cycle-by-cycle current limit outside PI window; safe duties on fault; watchdog tested.

- Calibration: dead-time, shunt gains/offsets, and Kp/Ki serialized with CRC; versioned to firmware.

Multichannel DDC (C66x or Multi-Core)

- Stripe channel banks per core; replicate coefficients; queue-driven DMA with pre-posted descriptors.

- Latency bands enforced with GPIO strobes; throttle nonessential tasks when yellow persists.

- Regression: BER/EVM under AWGN and phase noise; pass/fail gates per release.

10) Practical Selection Rubric (No Surprises)

- Instant-on? If yes, favor DSC/dsPIC; if no, include SHARC+/C66x for heavier math.

- Latency ceiling? µs → DSC/dsPIC; low ms → float or wide fixed with on-chip SRAM; relaxed → M33 with DSP pipeline.

- I/O discipline? PWM/ADC vs. I²S/TDM vs. queue ticks—pick one master domain and stick to it.

- Numerics? Lock Q-formats or math modes now; don’t mix them ad hoc later.

- Lifecycle? Prefer families with clear migrations; version presets/calibration from day one.

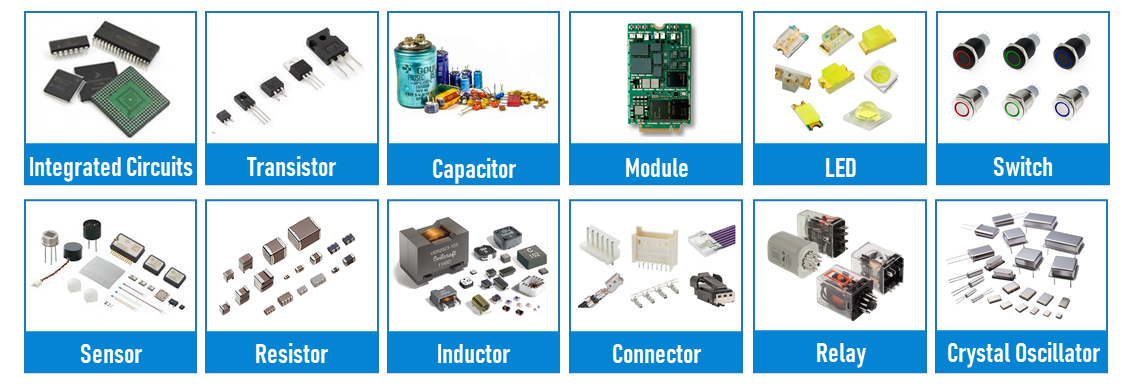

For sourcing support, long-term availability tracking, and vetted alternatives across device families discussed in this guide, visit YY-IC integrated circuit.